# BIPOLAR JUNCTION TRANSISTORS

A semiconductor device consisting of two p-n junca formed by sandwitching either p-type or n-type semiconductor who a pair of opposite types is known as a

It is also known as Bipolar June? transistor (BJT) since its operation depends upon the intereaction of both the majority and minority coerciers. is seen than I you

- Merits: (1) higher efficiency

- (ii) more mechanical strength

- (111) light in weight

- (iv) Smaller in size

- (v) smaller pour consumption etc: 1000000

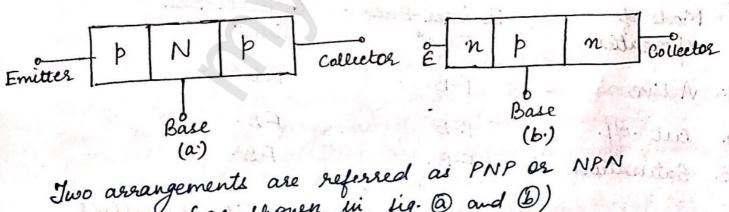

## CONSTRUCTION OF TKANSISTOR

It consists of two PN-june diodes, which are remented back to back or front to front In other worde, it may either have a N-type semiconductor sundmitched Upo tuo P-type semiconductore or a P-type semiconductor inserted life two N-type semiconductors.

Two arrangements the fig. (as showen in fig. (a) and (b) transstors (as showen in fig. (a) muse obelientes in section modes where on the

and offer to production to transition must operate in

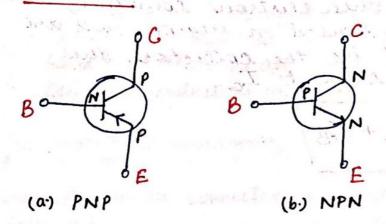

The BJT (PNP or NPN transister) has three regions emitter, base and collector and having two junc's i.e. emitter-base and collector-base.

- 1. EMITTER: This region is the heavily doped legion as compared to have and collector. The size of emitter is more than base but less than the collector

- 2. BASE: The size of lease region is entremely small, it is less than emitter as well as the collector. The doping intensity of base is also less than emitter and collector.

- 3. COLLECTOR: The collector terminal is moderately doped, and the size of collector negion is slightly more than enitter negion.

#### BJT BIASING \*

Different modes of transister opereation depends upon the bias cond of each of the two junchs namely, emitter have and collector-base junch.

| Mode of<br>Opereation |            | Emitter-Bace<br>Junc <sup>n</sup> | June" |  |

|-----------------------|------------|-----------------------------------|-------|--|

| 1                     | Active     | F-B.                              | R.B.  |  |

|                       | cut-off    | R-B                               | F-B.  |  |

|                       | Saturation | F·B·                              | FB.   |  |

\* In Amplifiers and Oscillatore circuits, transistors

must operate in active mode, whereas in Snitching

and other logical circuits, transistors must operate in

either cut-off or in Saturation mode.

Circuit Symbols of PNP and NPN bipolar transistors:

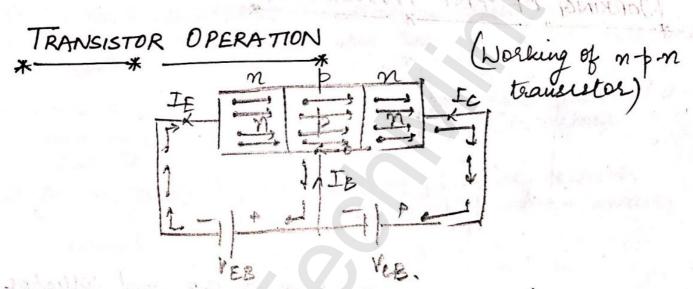

1. An n-p-n transietor circuit is shown in abone fig. Emitter. Base junc? is F.B. while collector-base junc? is R.B.

The F.B. Noltage VEB is quite small whereas R.B. Voltage VcB is considerably high. As Emitter-base junch is F.B. a large no. of electrons (majority carriers) in the exhitter are pushed towards have This considerables the emitter current IE

when these electrons enters the p-type material (Base) they tend to combine ewith holes, since the lease is lightly doped and very their, only a few electrons ( less than 5%) combines with holes to constitute the lease current 'IB

see the premaining electrons (more than 95%) diffuse across the thin base region and mean the collector space charge layer. These electrons combines under the influence of +vely beased n-negion and are attracted or collected by the collector. This considers collector cirrent Ic

IE = Ic + IB

WORKING OF PNP TRANSISTOR

In this the emitter-hase junc" is FB and collectorlease junc is R.B. VEB is quite small whereas VCB is considerably high As the emitter-hase junc" is F.B. a large no. of holes in the emitter are pushed lowards the lease, which constitutes to IE. When these holes enters p-type material (base) they tend to combine with electrons. Since the base is lightly doped and very thin only a few electrons (less than 5%) combine with electrons to constitute base current. IB.

The remaining holes (more than 95%) diffuse across the remaining holes (more than 95%) diffuse across the thin wase region and reach the collector space charge layer, which constitutes to Ic  $I_E = I_B + I_C$

TRANSISTOR

\* Most of the beaucistose are npn type and not p-n-p type hecause in n-p-n transistose the current conduction is mainly due to electrone whereas in p-n-p transistors the current conduction is mainly by holes. As electrone are more mobile than holes we can have conduction in n-p-n transistors.

### TRANSISTOR CONFIGURATION

The BJT can be connected in 3 ways in a circuit as follows:

- (i) Common emitter (CE) configuration, in which emitter terminal is common by input (hase) and output (collector) circuits.

- (ii) Common Base (CB) configuration, in which base terminal is common left input (emitter) and output (callector) circuits

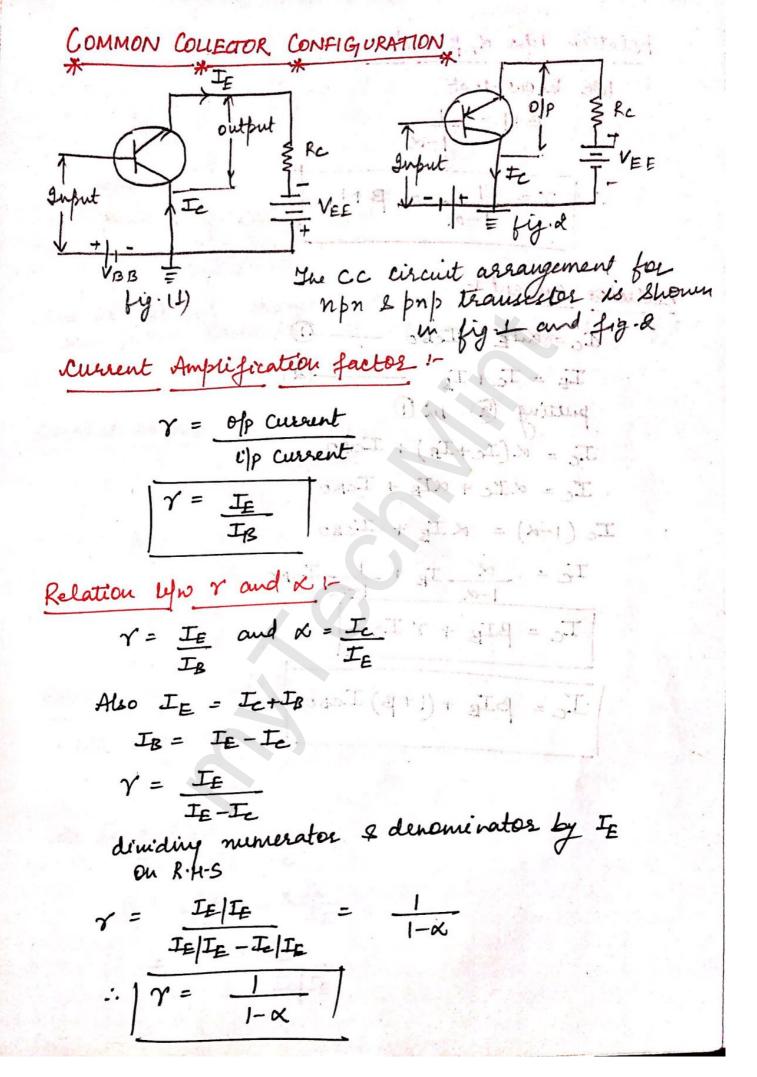

- (1)1) Common Collector(CC) configuration, in which collector terminal is common by input (base) and of (emitter) circuits.}

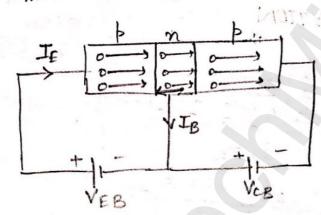

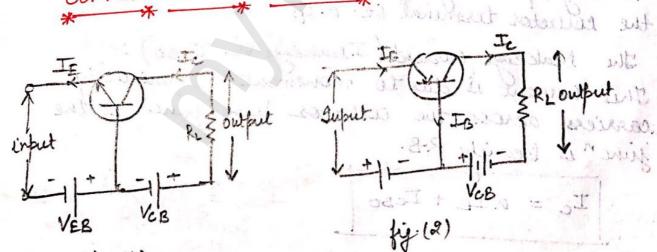

COMMON BASE CONFIGURATION

The common have circuit allangement for np-n transistor and p-n-p transistor is shown in fig. (1) and (2)

0) A live in percentage of

Current Amplification factor (x): (Katio of of current to

& is defined as the nation of mange in collector current to change in emitter current at constant VCB.

$$\alpha = \Delta I_c$$

$$\Delta I_E | v_{cs} = constant$$

We know that,

$$\Delta I_{E} = \Delta I_{e} + \Delta I_{g}$$

$\Delta I_{E}$

$\Delta I_{E}$

Practical Values & & in Commercial hancutore is 0.95 to (111) · CENTINON (2)

termare le Comme

the BIT some the colonestic

in Common environ. In

Circuits.

Christian Residen

#### Collector Current :-

Total collector current Consists of !-

- i) A large percentage of emitter current-weat reaches the collector terminal ie & IE

- (11) The leakeage current (I hakeage or IcBO):-This current is due to movement of minority carriers across we collector have june? as the junc " is beauty R.B.

transition and prophermentaries in Marie in pray (1) and (2)

toBo = Collector to have preverse saturation current. The examinations beaut assurgered for more

Relation left

$$\alpha$$

,  $\beta$  and  $\gamma$ .

We know that

$$\beta+1 = \frac{1}{1-\alpha}$$

$$\therefore \gamma = \frac{1}{1-\alpha} = \beta+1$$

#### collector current.

$$T_{c} = \alpha T_{E} + T_{CBO} - 0$$

$$T_{E} = T_{c} + T_{B} - 0$$

$$T_{C} = T_{C} + T_{B} - 0$$

$$T_{C} = \alpha (T_{C} + T_{B}) + T_{CBO}$$

$$T_{C} = \alpha T_{C} + \alpha T_{B} + T_{CBO}$$

$$T_{C} = \alpha T_{C} + \alpha T_{B} + T_{CBO}$$

$$T_{C} = \alpha T_{C} + \alpha T_{CBO}$$

$$T_{C} = \beta T_{C} + \gamma T_{CBO}$$

TE-IE

deraiding numerator a denominator by the control of the con

11/12 - 11/11

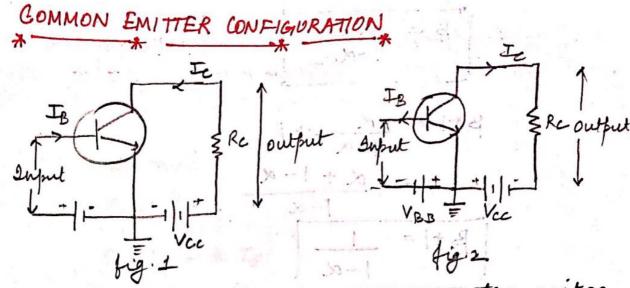

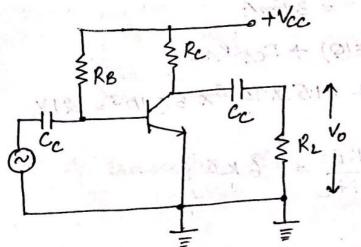

The CE circuit arrangement for np-n transistor and p-n-p transist of is shown in fig. 1 and fig. 2

$$\beta = \frac{T_c}{L_B}$$

Relation who do and B

we know-that

$$B = \frac{Ie}{IB}$$

and  $C = \frac{Ie}{IE}$

$$\Rightarrow \overline{I_E} = \overline{I_E} + \overline{I_B}$$

$$\overline{I_B} = \overline{I_E} - \overline{I_E}$$

$$\beta = \frac{\overline{I_C} \times \overline{I_E}}{\overline{I_E} - \overline{I_C}}$$

$$= \frac{\overline{I_C} \overline{I_E}}{1 - \overline{I_C} \overline{I_E}}$$

$$\beta = \frac{1}{1-\alpha}$$

$$\beta + 1 = \frac{\alpha}{1-\alpha} + 1$$

$$= \frac{\alpha + 1 - \alpha}{1-\alpha}$$

$$\beta + 1 = \frac{1}{1-\alpha}$$

$$= \frac{1}{1-\alpha}$$

$$\beta + 1 = \frac{1}{1-\alpha}$$

#### Collector current:

of IB=0, Ie is abbreviated as IEEO

ICEO = Collector emitter curaent with lease open

LUC LANGUE THAT

E Tet Is

June I In a CB configuration, the current amplification factor is 0.97 If the emitter current is 1mA, determine the value of have current

Soln

Ques The entitle current IE in a transistor is 3mA If the leakage current IEBO is 5MA and x=098 Calculate Ie and IB (for CB configuration)

$$I_E = I_C + I_B \circ \circ \circ \circ = SIA = SI$$

$$I_B = I_E - I_C$$

$$I_B = (3 - 2.945) mA \qquad SI = SIA = SI$$

$$I_B = (3 - 2.945) mA \qquad SI = SIA = SI$$

Ite - Jet I

I - II - II

Purs 3 In CB configuration the value of x = 0.98. A voltage deep of 49V is obtained across a receiver 5ks when connected in collector circuit Find In

$$T_{c} = \frac{4.9}{5 \text{ ks}} = 0.98 \text{ mA}$$

;  $K = \frac{I_{c}}{I_{E}}$

$T_{E} = \frac{I_{c}}{\alpha} = \frac{0.98 \text{ mA}}{0.98} = \text{ ImA}$

$$I_E = \frac{I_C}{\alpha} = \frac{0.98 \text{ mA}}{0.98} = \text{ImA}$$

Quest calculate the Value of emitter gurrent in a transcistor for which 13 = 40 and IB = 25MA (for CE configuration)

1m :0:0 - II .:

It the Limbour England

IC- 2.945m1

Ib = (3-2-945) mA

June 2 the epiths. Curren

Voltage is 10V. when a presistor RC = 1 K52 is

connected in a collector circuit, the Voltage drop

across it is 0.5V, For x = 098, determine

- (i) VCE

- (ii) IB.

$$\beta = \frac{\kappa}{1-\kappa} = \frac{0.98}{1-0.98} = 49$$

$$I_{B} = \frac{0.5 \, \text{mA}}{49}$$

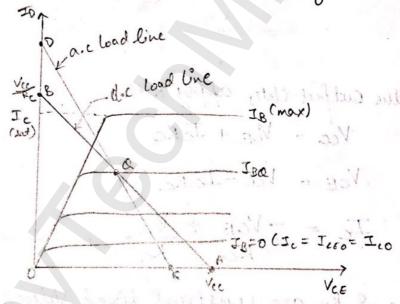

# TRANSISTOR LOAD LINES

It is defined as the local of operenting point on the outfut than of the transcitor. It is the line on which operenting point moves when ac signal is applied to the Craverstor

## de load line

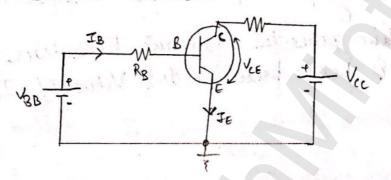

het us consider a CE amplifier circuit with base resistor RB and Collector relistor Rc

In the outfut cht, apply KVL:

$$T_c = \frac{-V_{CE}}{R_c} + \frac{V_{CC}}{R_c}$$

As, Vcc & Rc are Constant fixed Values i-e. Vcc is

Report 10

eg 1 D supresenté à straight line eg 7 y = mx+c

where

$$m = \text{slope of line} = \frac{1}{Rc}$$

where  $m = \text{slope of line} = \frac{1}{Rc}$

$\frac{V_{CC}}{Rc} = \text{intescept of line on the Vertical}$

RC Current axis of of there.

Consider, (i) when Ic = 0

VCE = Vcc; Cut-Off pt A

(ii) when  $V_{CE} = 0$   $I_{C} = \frac{V_{CC}}{R_{C}}; \text{ Laturation pt. B}$

The dc load line is given by joining pti A and B. The intersection of dc load line and characteristic cure gives the operating point (or B-point or quies cent point)

\* The de load line gives the dynamic behaviour of the Circuit and 8-point provides the Value of Ic and VCE.

#### ac load line

On applying the ac signal to the input, Q-point remains stable while transletor Veltage VCE and Collector current Ic Vary about the point.

If we draw ac load line, it has steeper slope than

the dc load line but two lines view intersect at the

9- point

The effective ac load Resistance, Rac =  $\frac{1}{Rac} = \frac{1}{Rc} + \frac{1}{RL} \quad (RL||Rc)$   $= \frac{R_1 + R_c}{R_c R_L}$   $= \frac{R_c R_L}{R_c + R_L} \quad (: R_c < R_L)$  = Rac = Rc = Rac = Rc

To draw ac boad line, max. VCE and max. Te is required in presence of ac signal

VCE = VCEB + IcB Rac (Cut-off point C)

Ic = Ica + VCER (Saturation point D)

Queel An CE configuration, Vcc = 10V, RL is BKS2. Draw dc load line. Determine the Q-pt for Fero signal if have current is 15UA and B = 40

Vcc = 10V RL = 8KS2 IB (Zero Signal have Current) = 15UA B = 40

for CE configuration

VCE = VCC-IERC

for VCC = 0

Ic = Vcc = 1.25mA (pt. A on load line)

for Ic = 0, VCE = Vcc = 10V (pt B on load line)

Zero signal collector Current

Ic= βIB = 40 x 15 x 10-6= 0.6 mA

$V_{CE} = V_{CC} - I_{eRL}$ =  $10 - 0.6 \times 10^{-3} \times 8 \times 10^{3}$ = 5.2V

:. Opereating point is (5.2V, 0.6mA) ons.

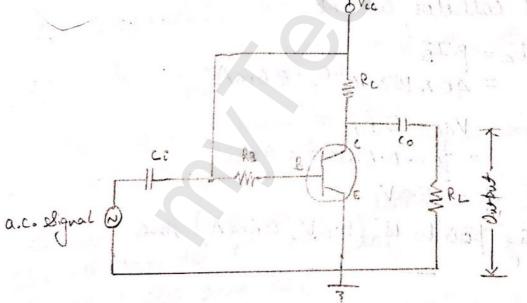

Pund. In a transistor amplifier as shown in fig., Rc = 8K2, RL = 24K2 and Vcc = 24V.

Draw the dc load line, determine the Optimum Operating point. Also draw- we are load line.

800: Given

$$Rc = 8 k\Omega$$

$RL = 24 k\Omega$

$Vcc = 24V$

(a)

$$I_{c}$$

(saturation), when  $V_{cE} = 0$

$$I_{c} = \frac{V_{cc}}{R_{c}} = \frac{24}{8\times10^{3}} = 3mA \text{ (point B on dc load line)}$$

(b) Optimum operating point: - hidway of the load line AB provides the optimum or max. operating point Ie(9) and VCE(9)

(c) In Ac-lood line

I (saturation) =

$$I_{E}(S) + V_{E}(S)$$

Rac

$I_{E}(S) + V_{E}(S) + V_{E}(S)$

and  $V_{CE}(Cut-GS) = V_{CE}(S) + I_{CO} Kac$

$I_{E}(S) + I_{E}(S) + I_{E}(S) + I_{E}(S)$

[Rac =  $I_{E}(S) + I_{E}(S) + I_{E}(S) + I_{E}(S) + I_{E}(S) + I_{E}(S)$

[Rac =  $I_{E}(S) + I_{E}(S) + I_{E}(S) + I_{E}(S) + I_{E}(S) + I_{E}(S)$

[Rac =  $I_{E}(S) + I_{E}(S) + I_{E}(S) + I_{E}(S) + I_{E}(S) + I_{E}(S) + I_{E}(S)$

[Rac =  $I_{E}(S) + I_{E}(S) + I_{E}($

A circuit is shown in fig. Analyze it for diff. sugious of operention.

Over (+5v) Ginen VBB = 5V VCC = 5V E P= 100 B = 100 RB = 50K52 RC = 2K32 RB = 50 KSZ (a) If transcitor operentes in active region  $I_B = \frac{V_{BB} - V_{BE}}{R_B} \qquad (V_{BE} = 0.7 V \text{ for Si})$ = 0.0 86 mA will an columnet grang will come Ie= BIB = 100×0.086 mA = 8.6mA Collector Voltage Vc = Vcc - JeRc = 5-8.6x2 emitter is grounded 90, transistes cannot operente in active negion (b) Consider the transmitor opereation in saturation

(b) Consider the -practice using the practice

$$V_{BE}$$

, sat = 0.8 V)

$$I_{B} = \frac{V_{BB} - V_{BE}, sat}{R_{B}}$$

$$= \frac{5 - 0.8}{50} = 0.084 \text{ mA}$$

$$T_{C} = \frac{V_{CC} - V_{CE, Sat}}{R_{C}}$$

$$= \frac{10 - 0.2}{2} = 4.9mA$$

$$= \frac{10 - 0.2}{2} = 4.9mA$$

$$T_{B, min} = \frac{T_{C, Sat}}{R} = \frac{4.9mA}{100} = 0.049mA$$

: transister will définately operate un Baturation enegion.

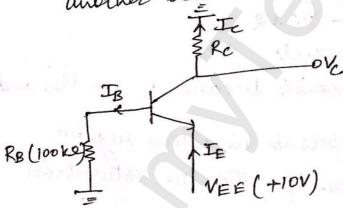

Que The p-n-p transistor in fig has B = 50. Find the Value of Rc to Obtain Vc = +5V. What happene to if the transistor is replaced with another transistor having 13=100.

RB = 100K52, VEE = 10V VBE = 0.7V ( m active mode) Vc = +5V Apply KVL in infut VEE = VEB + IBRB  $IB = \frac{V_{EE} - V_{EB}}{R_B} = \frac{10 - 0.7}{100} = 0.093 \text{ mA}$

Vi Value et V. 12 11

rinduct is green to

$$T_c = \beta T_B = 50 \times 0.093 = 4.65 mA$$

$$R_c = \frac{V_c}{T_c} = \frac{5}{4.65} = 1.08 \text{K} \text{S} \text{L}$$

(6) If the transistor is replaced by another one Class. 100 having 13=100

This shows that transister will operate in Saturation pregion as collector voltage is greater than have Holtage

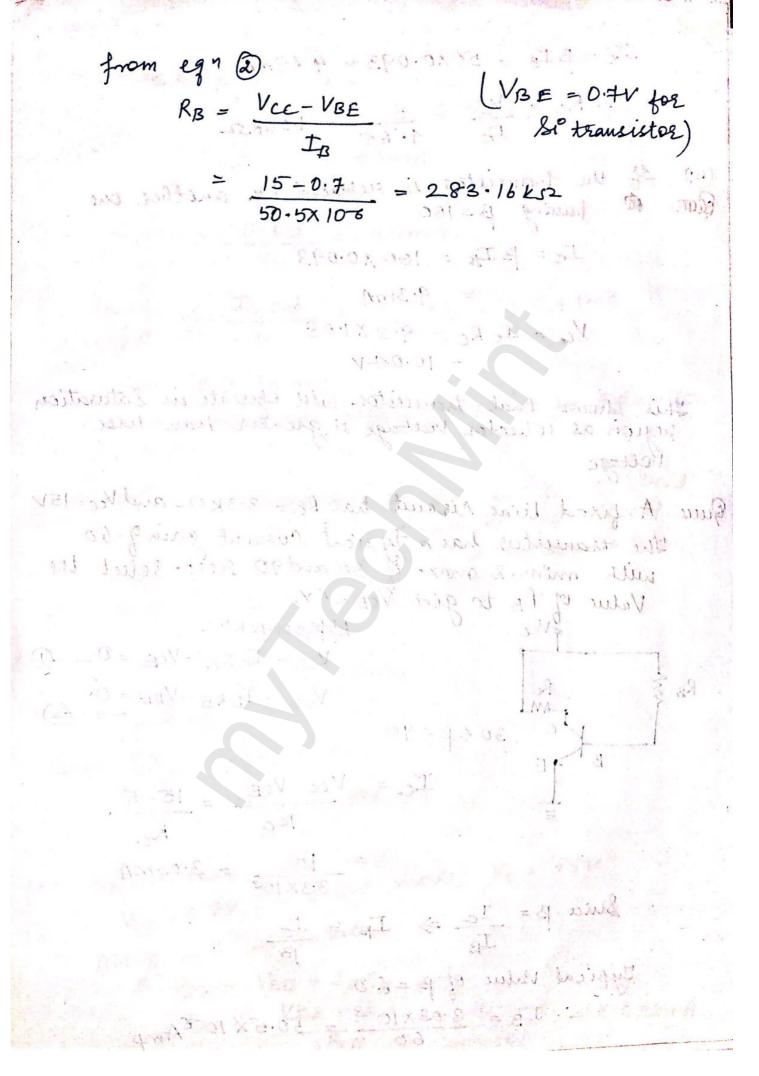

Ques. A fixed lucas circuit has Rc = 3.3 Ksz and Vcc=15V The transistor has a typical current gain of 60 with min. & max. of 30 and 90 resp. Select the Value of RB to give VCE = 5v.

Applying KVL

$$I_c = \frac{V_{cc-V_{cE}}}{R_c} = \frac{15-5}{R_c}$$

$$= \frac{10}{33\times10^3} = 3.03mA$$

Sina

$$\beta = \frac{I_c}{I_B} \Rightarrow I_B = \frac{I_c}{\beta}$$

Typical Value of

$$\beta = 60$$

:.  $EB = \frac{3.03 \times 10^{-3}}{60} = 50.5 \times 10^{-6} Amp$

## \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

The collector current (or current gami, Bdc) of a transietor strongly depinels on two parameters

(1) Transistor

(ii) Tempereature

In a circuit, if transistor is preplaced by another, then The and VCE also change. Similarly Ic (OS Bdc) Varies with hemp. Circuit analysis of transistor industes that Bdc hicreases hith increasing temp and decreases with decreasing temp.

50, for faithful Amplification of input signal, a-point must hemain fixed, irrespective of these nariations. This process is known as stabilization.

Thermal Runaway is the process in vehich collector current increases with temp. As collector current increases, temp of the junc increases due to power dissipation (I'R) at the collector june? The increases the temp. DT encreases the collector current therby further increasing in the temp. As a result & self-distruction of transistor is possible

This process is cumalatine and fast and may cause the transmites to be destroyed or damaged. Therefore, in any transistor circuit, this effect should be avoided.

4 4 1/2 3 1/2

INTERNATIONS OF

In a transitor cht, it is necessary and desirable to keep Ic and VCE constant so that 0-point becomes btable! These are 2 methods to make operenting point fixed.

Leavening Rendered

U) Stabilization (ii) Compensation

In the first case, bearing cht is used and in and case temp. sensitive devices such as diodes, thermostors etc. are used to compensate the Variations in Voltages & Currents to keep opereating point (ICO, VCEO) constant.

Stability factor, 5 is defined as the Change in of Collector Current with respect to Ico Current by keeping Bdc and VCE constant.

$$S = \frac{\partial I_c}{\partial I_{eo}} \rho dc$$

and  $V_{cp} \propto \Delta I_c$

In CE Configuration,

Ic = Bdc IB + (L+Bdc) Ico

diff exentiating with respect to Ic

$S = \frac{1 + \beta dc}{1 - \beta dc}$  for a circuit in which  $\frac{1}{2 I_c}$   $\frac{1}{2}$   $\frac{1}{2}$

#### EBER-MOLL'S MODEL

Eber-Moll Model is called the coupled diode model which describes the dc char. ga transistor. This model generalizes the behaviour of a transistor by considering the normal and viverted mode of operentions.

Let us consider the PNP transistors,

JE E C. Te

P P P C B E

P Is (fig. 1) (Normal Operation) (Inverted operation)

During normal opereation, VEB is F.B. and VCB is R.B.

IEN = IEO (e EB/V-1)

and I cn = QUAN ON IEN (eVEB/VT-1)

where  $I_{E0}$  and  $\alpha_N$  are reverse Saturation currents at emitter junch and current amplification factor in normal operation.

IEN and Ich are entitler & collector current resp. in normal mode.

Under inverted mode, VEB is R.B and VCB is F.B.

$I_{CI} = -I_{CO} \left( e^{V_{CB}/V_{T}} - I \right)$   $I_{EI} = \alpha_{I} I_{CI} = -\alpha_{I} I_{CO} \left( e^{V_{CB}/V_{T}} - I \right)$

Ico and KI are everee saturation currents of diode at collector junch and current amplification factor in inverted mode respectively.

IEI and IcI are emitter and collector current rusp in the inverted operation.

WEAR (CIVE)

IE = IEN + IEI = IEO (eVEB/V-1) - & I ICO (eVCB/V-1) and Ic = Jen + Ici -Ico (e VCB/VT-1) + XN IEO (e VEB/VT-1) eg " D and @ are known as Eber-Moul equations In contains two terms, 1st represents diode eg " at entitler junc" and and represents a current controlled Similarly, fruit terms of Ic represents the diode egn at collector junca and Red term is for current controlled by emittee diode. by collector diode. IEN = IEO (eVEB/VT) and liver is say >Eber-Mou Model of a p-n-p transcitor Icn= dnIE Eber Moll-Model for normal P-N-P LETTE CULTURE Opereation.

Little A Transfer and I

For a p-n-p traveistor in normal mode, C-B arrangement, VEB = F.B. and VCB = R.B.

Hence IeI = 0 (collector-base divode behaves

and IEI = 0

and IEI = 0 and IEI = 0 Thus Eber-Holl equinalent circuit is shown in liq. 3 Also  $\propto_N I_{EO} = \alpha_I I_{EO}$  (Acc. to Reciprocity cond of BJT.) :. IE = JEO(e VEB/VT-1) - XI [XN JEO eVEB/VT-1)-IC] = XIIC + (1-XN XI) IEO (eVEB/VI) => IE = NIIC + IREO (e VEB | VT -1) where  $I_{REO} = (1 - \alpha_N \alpha_J) I_{EO} = Reverse saturation emittee current$ Similarly, I'C = KNIE - IRCO ( e VCB/VI-1) Where IRCO = (1-xwx,) Ico as in action mode |VCB|>>VT :. Ic = XN IE + Ico Standard Current eg 9 transiel or in active configuration

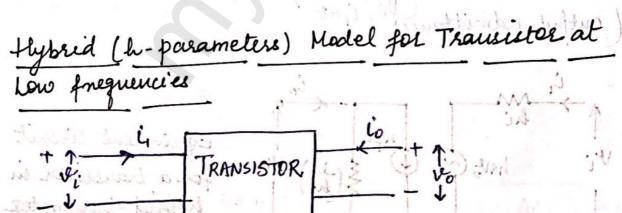

# MODELING OF BJT AS AMPLIFIER AT LOW

There are three small signal models for BJT used in the analysis and design of transitor amplifiers:

- (1) h- parameter model

- (ii) re-model

- (III) hybrid A model.

- \* h- parameter model is preferred over the other transitor models due to its advantages as under:

The firly + Early

to = he Cithe U.

- (i) At low audio freq. the h-parameters are real numbers because all witernal capacitances can be neglicted.

- (ii) If h-parameters for one configuration is known, it can be obtained for other Configuration easily by a simple conversion.

- (iii) h-parameters can be measured easily from the transister de Char.

- (iv) h- parameters model is independent of types of the transister (NPN or PNP)

In hybrid parameter représentation; the input current and output voltage are taken as indépendent

Variables reluseas input voltage and output current as dependent vasiables Vi = \$4(Ci, Vo) and in lo = f2 (li, vo) The No egrs are 1-Jahon ... w Vi = hill + have io = hp 1, + ho Vo hypoid or madel. The h-parameters can be defined as! (i) hi =  $h_{11} = \frac{v_i}{v_i}$  (ohms); output short-circuited (input impedeance) (ii)  $h_{R} = h_{12} = \left(\frac{V_{i}}{V_{o}}\right) i_{1} = 0$ ( neverse voltage gain) Emple Remerciation. (111) hf =  $h_{21} = \frac{l_0}{l_1}v = 0$ (forward current gain) (iv) is became los model s (iv) ho = h22 = (10) i input open-ciscuited ( output admittance) Hupsed ( b. - pressamens.) was frequencial Equivalent circuit for a traveritor in hybrid-parameter representation current our culput caltage are tulien as independent

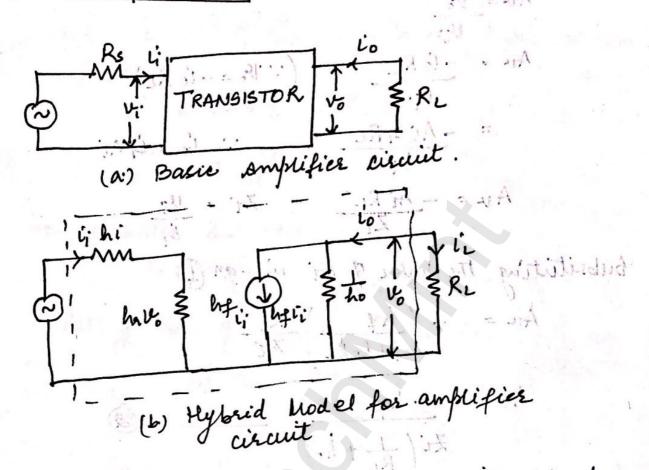

Analysis of a transistor Amplifies circuit wing hybrid h-parameters

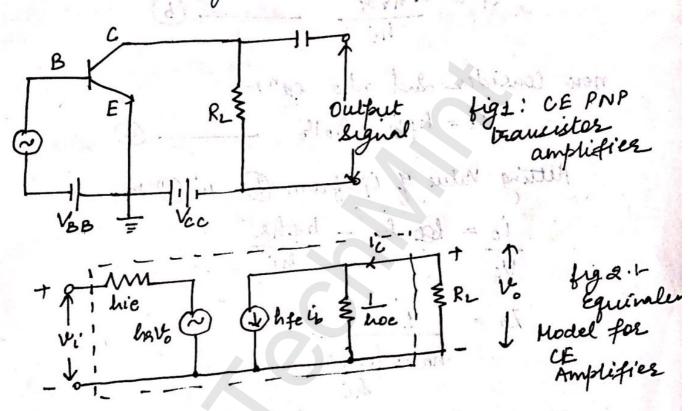

Atransietos amplifies consists of a transcetos, load resistos, beas supply and if alternating signal. Its two port now is shown in fig. 1 and its equinalent hybrid model is shown in fig. 2

(ii) Valtage gam (Aw) !=

$$Av = \frac{V_0}{V_i}$$

$$Av = -\frac{10R_L}{V_i}$$

$$= -Ai C_i R_L$$

$$V_i = \frac{V_0}{V_i}$$

$$Av = -\frac{A_i R_L}{Z_i}$$

$$\frac{V_0}{V_i}$$

$$\frac{V_0}{V_i}$$

$$\frac{V_0}{V_i}$$

$$\frac{V_0}{V_i}$$

$$\frac{V_0}{V_i}$$

$$\frac{V_0}{V_i}$$

$$\frac{V_0}{V_0}$$

$$\frac{V_0}{V_0} = -\frac{V_0}{V_0}$$

(1V) Outfut Impedeance: (Zo)!- (RL - ) oo and Vi-0 = i, hi + havo now consider and no egn; Petting Value of vi from ( in ( 1kg ho - hthe ho - heht If he is very small and hi is large

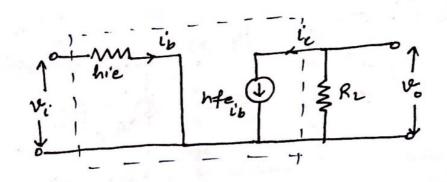

h-parameters Analysis of a Common-Emitter Amplifier

Let us consider a CE amplifier Circuit as Shown in fig 1. The h-model for CE configuration is shown in fig. 2

In circuit of fig. 2, capacitance C is neglected because impedeance is assumed to me zero once the given enange of freq. has is also neglected becomes most of the transmitors give very small value (~10<sup>-5</sup>) hoe is neglected as it is of the order of 10<sup>-5</sup>mho. hoe is neglected as it is of the order of 10<sup>-5</sup>mho. Hence it has very large value of hoe is shown in the equivalent circuit thus obtained is shown in the equivalent circuit thus obtained is shown in fig. 3.

(ii) Voltage gain Ave =

$$\frac{V_0}{V_i}$$

$$= \frac{-i_c R_L}{hie Ub} = \frac{-h_{fe} U_b R_L}{hie U_b}$$

$$= \frac{-h_{fe}}{hie} R_L$$

(111) Power gain, Ape = [ current gain |

$$\times$$

| Voltage gain | =  $\frac{h^2 re}{hie} \times R_L$

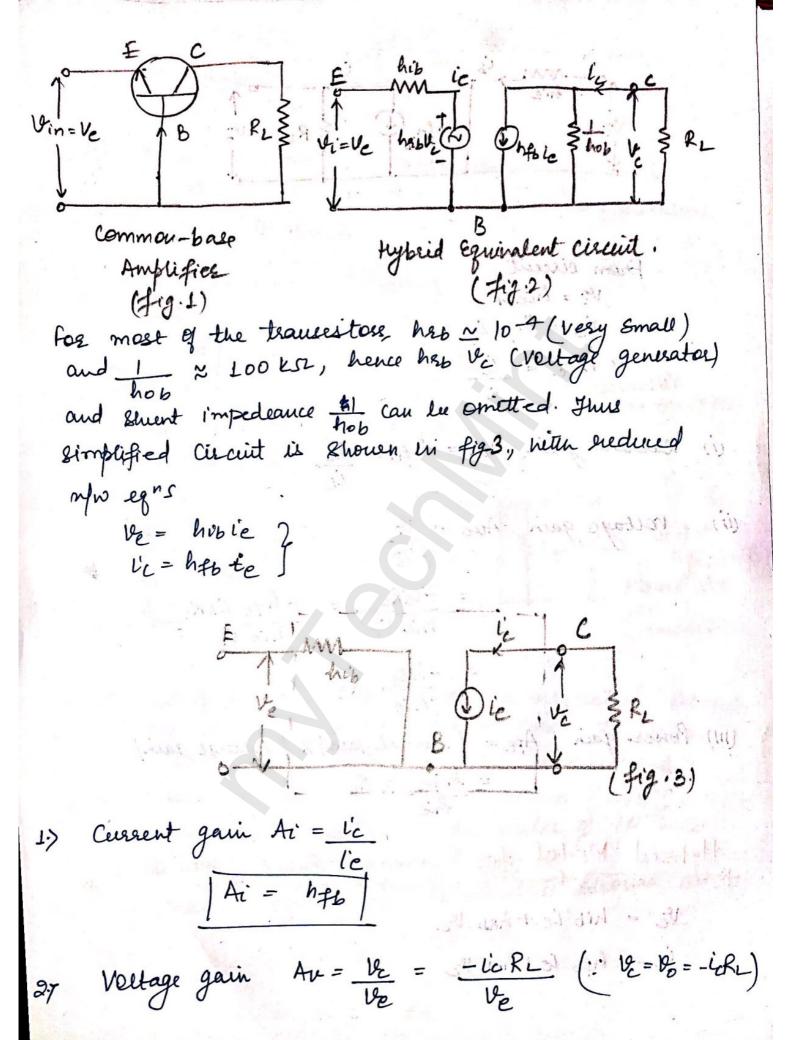

Hybrid Model for Common-Base Amplifres

where

$$\frac{hfb}{hib} = g_m = transconductance$$

$$Au = -g_m R_L$$

(iii) Power gain 1-

$$Ap = |Ai||Au| = \frac{h^2 + bR_L}{hib}$$

In Common-has Configuration  $Ai \le L$ ,

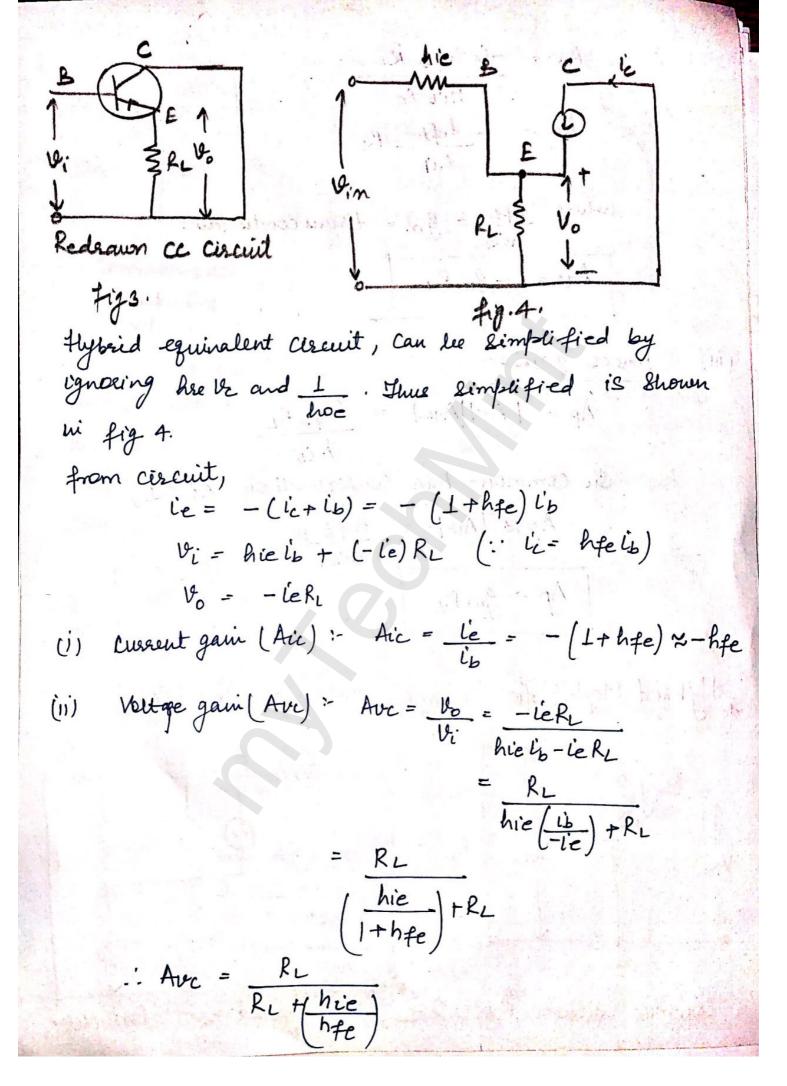

Hybrid Model for Common Collector Amplifies

Non St. Vin Experis Res 100

Common Collector Amplifies Byteid equivalent che.

# FIELD EFFECT TRANSISTORS

A field effect transister is a unipolar denice in which current conduction is only by one polarity carrier (i.e. majourity carrier). Flow of current is controlled by electric field.

FET can be categorized into two types:

- (1) Tunction field effect transistor (TFET)

- (11) Metal exide semiconductor field effect Traverst or (MOSFET).

- \* FET has many advantages over BJT!-

- (i) In BIT output so current is controlled by infait cuerent, so names as current controlled device, while FET is voltage controlled device.

- (ii) The input to BIT amplifies involves a F.B. PN-jimon with low resistance, while input to FET involves a sieverse luased PN-june with very high resistance.

- (iii) Thermally stable than BJT

- (iv) Less noise than BJT.

- \* The main drawback of FET is relatively small gain B.w. product

JUNCTION FIELD EFFECT TRANSISTOR (JFET)

It can be of two kinds

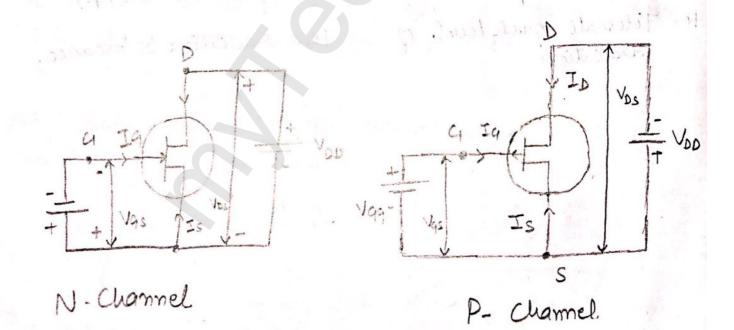

- (i) N-channel. It is made of N-type Semiconductor (i) P-channel. It is made of P-type Semiconductor

\* A J'FET is a three terminal device namely. Source drain and gate terminal. It consists of a P-type of n-type silicon bar containing two P-N junc's as shown in fig. The two p-n junc's forming diodes are connected internally and a common terminal called gate is taken out Drain (D) Source (s) Ros Drain (D) Source(s) Channel Source P-Channel JEET

- Li Source 1- Germinal through which majority carriers enter the bac.

- Deani :- yerminal through which majority Carriers Leave the war

- 37 Gatel- form P-N junc's

- 47 Channel Space Mus two gotes through which mojority Carriers pass.

the leving pain

### CIRCUIT SYMBOL & NOTATION

feeled cottions is notife decision

light tifud intertance

1. Unipolar device

a. Veltage controlled dewie

3. Low noise level

4 High input impedeauce

5. Gain is characterstised by transconductance

6. Better turnal Stability

7. High power gain

& Fabrication of FET is simple.

9. Smallu lize, longer life, high efficiency

10. Tolereate much level of tradication

Bipolas device

Current Controlled device

witch the Fare

fligh noise level

Low input impedeance

Gain is characterchiced by Voltage gain | Current gain.

less thermal Stability

Loro power gain

Fabrication is little tough

less life I less efficiency hi compassision to JFET

Less radiation to because.

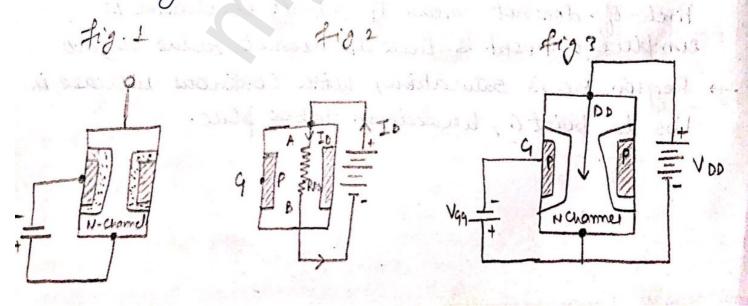

\* Suppose that gate & has been R.B. and drain battery

VDD is not connected. Depution layer formed symmetrically

about the gates (as in fig.1).

\* Further Consider drain battery connected & gate bottery nemoved. Suppose RDS is resistance from drain to lousco. 30, due to current Is there will be uniform vertage drop from drain to source Consider potential at two points A and B. (VA) VB) (as shown in fig. 2)

\* Now in proper working of JFET Both hatteries VGG & VDD Connected Simultaneously Reverse livesing effect On P-N junch is stronger near drain too than near source. One to this reason penetration of A is more than B.

when two depletion engion touch each other & To becomes zero.

NOTE: Suice - ve gate Vertage Control Current so, et is Called Vertage Controlled device.

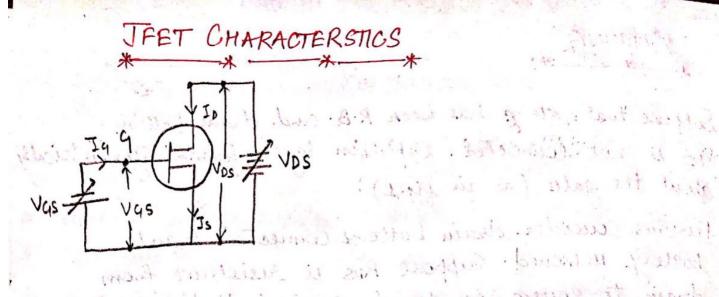

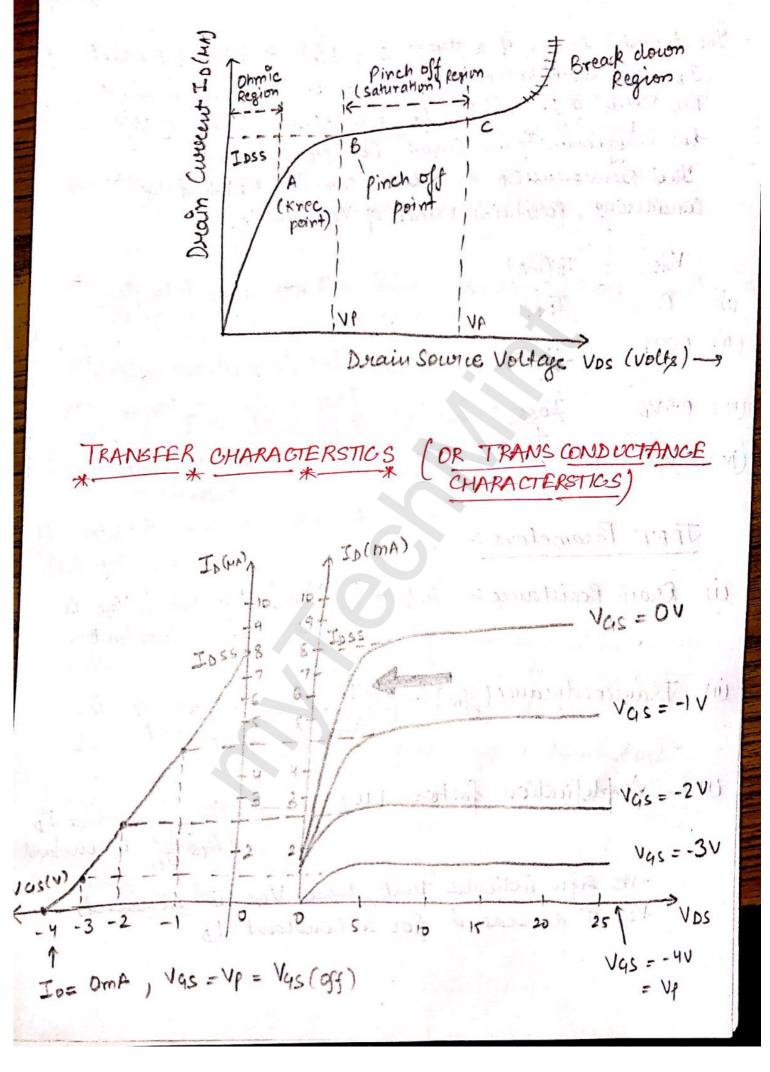

\* Types of Static Characterstics:

- -> Vas = 0 (Gate is shorted to source)

- -> VDS = 0, lunce ID = 0

- As Vos 1, Is 1 linearly upto A (knee point)

- Increasing Is, surverse lives the gate junc and Channel begins to constrict

- As Vos vicreases. Is heaches to point B. (pinch-off point)

- -> At pinch off point Channel is more or less belocked

- Pinch-off is defined as the min. drain to source Voltage where the drain consent approaches a constant Value. Pinch-off does not mean Is cut off or channel is

- completely closed & hence Ip doesnot reduce to zero

- -> Region BC is saturation, heith continous miceease in VDS to point C, besealedown takes place.

The transfer char. of a JFET is a plot of output Current Is VS input voltage, Vas for a constant. By reading the Value of Is and Vas for a particular Value of Vos the transconductance curene can be drawn. This curene using 4 points can be obtained by considering following Values of Vas and Is.

(ii) Transconducance (gm): - (

$$\frac{\partial J_D}{\partial V_{GS}}$$

) v<sub>DS</sub>, where V<sub>DS</sub> is constant

### JFET Applications!-

- (1) JEET are used in conscade amplifiers in test and measuring devices, because of low level noise.

- (ii) The Can be used in Vottage Variable resistes (VVR) rescause of Variable resistance in Ohmic Region.

- (ii) They are used in low freq. amplifices (heasing aid etc.), because of low coupling capacitos

- (iv) They can be used in analog Smitches

- (V) They have very high power gain.

- (4) They one preferred in computers and other Ic's because of Small Sizes.

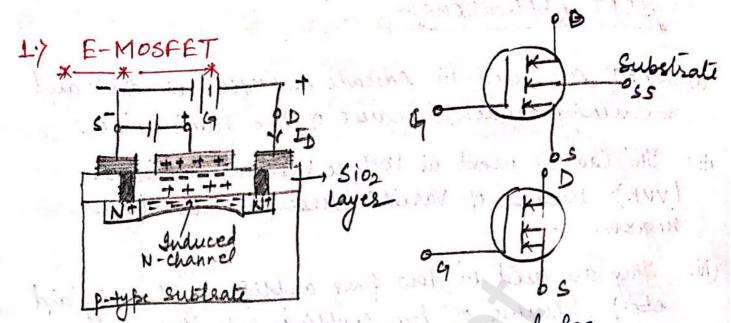

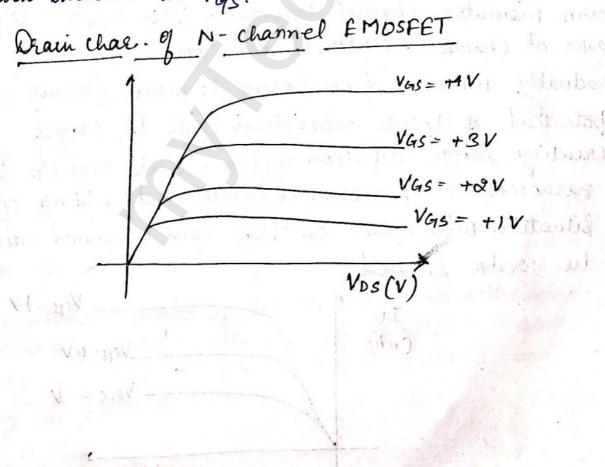

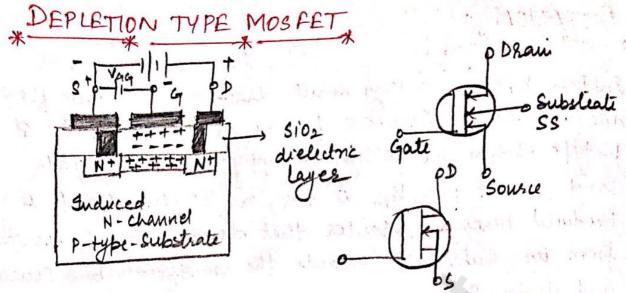

## METAL OXIDE SEMICONDUCTOR FET :-

In this denice, gate good consists of metal and helpisolated from channel by inserting a thin layer of Siog insulator For this neason they are also called IGFET'S (Insulated Gate field Effect transistes)

Types :-

17 Enhancement Type

27 Defection Type.

Mosfet's donot have continous Channel for Conduction.

Construction: A lightly doped P-type Remiconductor is taken as a subtrate and two lightly doped Nt type sugrous diffused in it. One N-sugron is source and other is drain D. There are Repeated by distance Imm. A thin layer of insulating material i.e. (3102) is then deposited leaving only two holes for connections to the source and the drain. A thin layer of the aring only two holes for connections to the source and the drain. A thin layer of to a metal is now deposited oner the sign This metalic layer acts as gate, insulator (5102) and Semiconductor chaunel together forms a Hel frate Capacetor which suplace the P-N fine of JFET. Input Impedeance is very high due to insulating layer (1010-1015).

Suppose Vqs=0, a very small drain current will from due to minority carriers present in the Substrate of P-type when the Veltage is applied at the gate Wort. Source i-e. Vqs is the, an electric field is produced through capacitos that draws minority carriers from the substrate towards the n-negion by source and drain forming channel of N-type material ie the potential at the gate induces off. Charges between sources and drain vehice acts as N-channel. Hence this channel is renown as induced channel. As a much conductinity increases and current froms through this channel. Therefore deam current strongly increases with increase in Vqs.

when VGS = 0, a very small drain current flows due to minority Carriers in p-type subtrate where we Vertage is applied at the gate wort. Sousce VGS becomes tre, thus an electric field is produced which is perfendicular to the capacitor. In this process free carriers present in the substrate are moved away from mendator-channel boundary. This create defletion layer at channel. Width of defletion layer at gradually increases from source to drain because polential of points meas drain neith he larges creating larger defletion neidly. This results in narrower of the channel width and a pinch off situation will arise. In this cond channel will be wedge shaped.

$V_{QS} = IV$   $V_{QS} = 0V$   $V_{GIS} = -V$   $V_{DS}(v)$

#### BOOLEAN ALGEBRA AND MINIMIZATION TECHNIQUES Berlem Expression - Send Es

A+C+A

1 = 1 1-1

TRUTCHOGY THE

(11) a. a. = a.

0.0 = 7HT (II)

BOOLEAN POSTULATES

#### 1. COMMUTATIVE LAW !

3. Distributione Law 1-

Identity elements 4.

(1)

$$a \cdot 1 = 1 \cdot a = a$$

Complement Law: -5.

(ii)

$$a \cdot \overline{a} = 0$$

PRINCIPLE OF DUALITY

In boolean algebra if the dual of any expression is desired simply replace every to with !! and every '.' with "t' or every 'o' with 'L' and every 'I' with o'

5.47 = 10 "

1 + 0.0

www.mytechmint.com

Scanned with CamScanner

. 761.0.

0

. 6.

S.NO. Boolean Expression

THE EFFOR PERSONAL AND DIRECTOR OF THE PARTY OF THE

A+0 = A 1.

2 A+1= 1

3. A+A = A

4. A+ A = 1 Dual Expression A.1 = A

A.O=O WALLEY

AA = A

A. A = OW BYTHOUMING & e as art - l+a

BOOLEAN THEOREM

1. TAUTOLOGY LAW:

(i) a+a = a

(ii) a.a = a

Proof! - (i) L.H.S = (a + a)

$= (a + a) \cdot 1$

= (a+a) (a+ā)

= a + a.a

= a = RHS

L. H.S = a.a (11)

= a.a +0

· accompatat

= a.a + a.a

(4) a.b = L.a. & ASSCRIPTIVE 1842: (a) a+(1+c) -(2+1) +c

$\alpha \cdot (1 \cdot n) = (n \cdot n) \cdot n \quad \text{ell}$

s. Wistirbutar town

DAN (dt 1) - (D. d) +,0 (0)

a. (1.6) = (1.6)+

Tolerstilly. Climante

SiL

0.1.=1.0 · (11)

5. Complyment have in

a+ 2 = 1 (1)

> Q. a = 0 111

LINGTELL OF DE

In libertian affection is the dual (a+a) a it is con Eno = · at = R.H.S. usus assider within & harris is

EVERY " LIEL " OS EVERY O' LILL I and

every I' mich o

(i)

$$a+L=L$$

Proof 1- (i)

$$k \cdot H \cdot S = a + 1$$

=  $(a + 1) \cdot L$

=  $(a + 1) \cdot (a + \overline{a})$

=  $a + 1 \cdot \overline{a}$

=  $a + \overline{a} = L = R \cdot H \cdot S$

THE RESERVENCE

arab = a.L.

(iii) L.W.S = a+ a 6

KH3 & a. (K+L)

6. Q. J+ Q. b

315-6 0 0

V. a. (a. el.) . a.

in arabea.

(ii)

$$k \cdot H \cdot S = a + 0$$

=  $a + (a \cdot \overline{a})$

=  $(a + a) \cdot (a \cdot \overline{a})$

=  $a \cdot L$

=  $a = R \cdot H \cdot S$ .

### 3. INTERSECTION LAWS 1-

(ii)

$$a \cdot 0 = 0$$

(i)

$$k \cdot H \cdot S = a \cdot 1$$

=  $a \cdot (a + \overline{a})$

=  $a \cdot a + a \cdot \overline{a}$

=  $a + 0 = a = R \cdot H \cdot S$ .

(ii)

$$k \cdot H \cdot S = \alpha \cdot 0$$

=  $\alpha \cdot 0 + 0$

=  $\alpha \cdot 0 + \alpha \cdot \overline{\alpha}$

=  $\alpha \left(0 + \overline{\alpha}\right)$

=  $\alpha \cdot \overline{\alpha} = 0 = R \cdot H \cdot S$

H. AFBSOR PTION LANDS:-

(ii)

$$a \cdot (a+b) = a$$

(iii)  $a + ab = a$

(iv)  $a \cdot (\overline{a+b}) = a \cdot b$

(iv)  $a \cdot (\overline{a+b}) = a \cdot b$

(iv)  $a \cdot (\overline{a+b}) = a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot (a+b) = a \cdot a \cdot b$

(iv)  $a \cdot$

$$\overline{a} = a$$

$$k \cdot H \cdot S = \overline{a} \cdot A$$

$$= \overline{a} \cdot A \cdot A$$

$$= (\overline{a} \cdot a) + (\overline{a} \cdot \overline{a})$$

$$= \overline{a} \cdot a + \overline{a} \cdot a$$

$$= (\overline{a} + \overline{a}) \cdot a$$

$$= (\overline{a} + \overline{a}) \cdot a$$

$$= 1 \cdot a$$

$$= 1 \cdot a$$

$$= a = R \cdot H \cdot S$$

(i)

$$a+b = a.b$$

V. imb.

Proof-1- (i)

$$a+b=a\cdot b$$

Proof-1- (i)  $a+b=a\cdot b$

Sufficient to prone that,

do the proof from book

Ques 1. Find the dual of the following boolean expression: (1) A+AB=A Oual expression of A+AB = A. (A+B) EReplace + with '. and '. with +'?

(ii)

$$A + \overline{A}B = A + B$$

$A \cdot (\overline{A} + B) = A \cdot B$

Jues. Prone the following expressions:

$$= (A+B) = R \cdot H \cdot S$$

$$= (A+B) = R \cdot H \cdot S$$

$$= A \cdot D$$

(11)

$$ABCD + ABCD = ACD$$

$1.H.5 = ABCD + ABCD$

$= ACD (B+B)$

$= ACD = R.H.5$

(III)

$$AB + \overline{A}C + BC = AB + \overline{A}C$$

$L \cdot H \cdot S = AB + \overline{A}C + BC$

$= AB + \overline{A}C + (A + \overline{A}) BC$

$= AB + \overline{A}C + ABC + \overline{A}BC$

$= AB + ABC + \overline{A}C + \overline{A}BC$

$= AB + ABC + \overline{A}C + \overline{A}BC$

$= AB(1+C) + \overline{A}C(1+B) = AB + \overline{A}C = R \cdot H \cdot S$

June Limber of

(iv)

$$(X+Y+XY)(X+Y)(XY)=0$$

$K+S=(X+Y+XY)(X+Y)(XY)=0$

$=(X+Y+XY)(X+Y+0)(XY)$

$=(X+Y)+XY)(X+Y+0)(XY)$

$=(X+Y)+XYY$

$=(X+Y)+XYYY$

$=(X+Y)+XYYY$

$=(X+Y)+XYYY$

$=(X+Y$

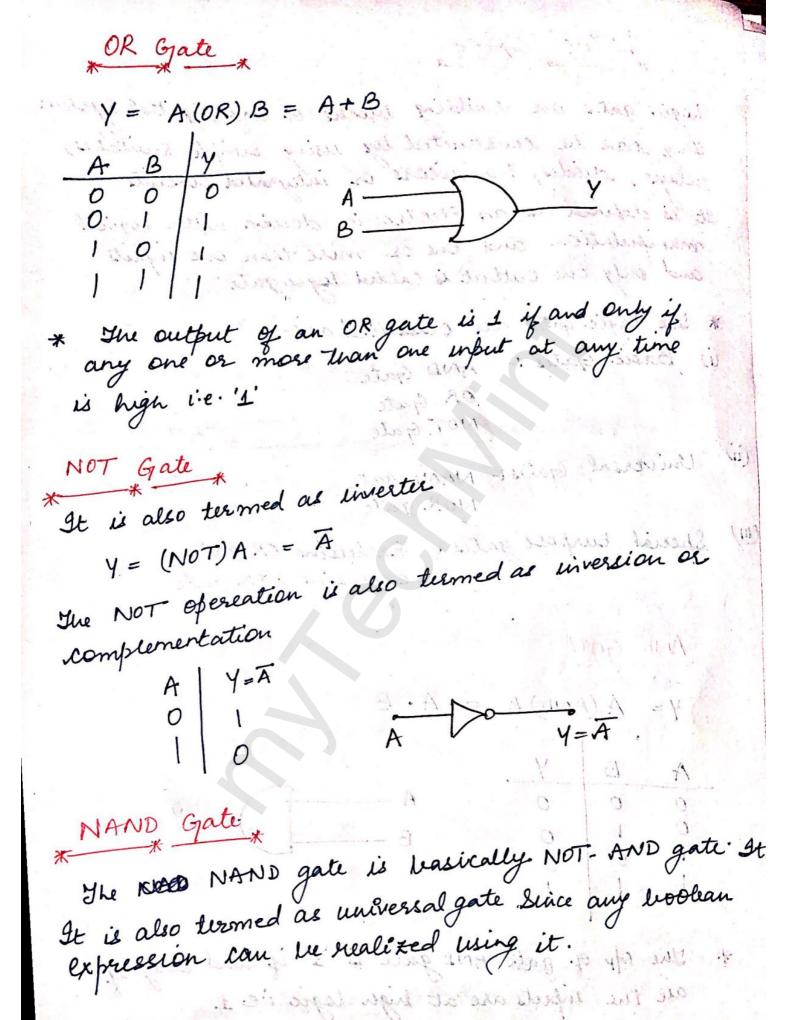

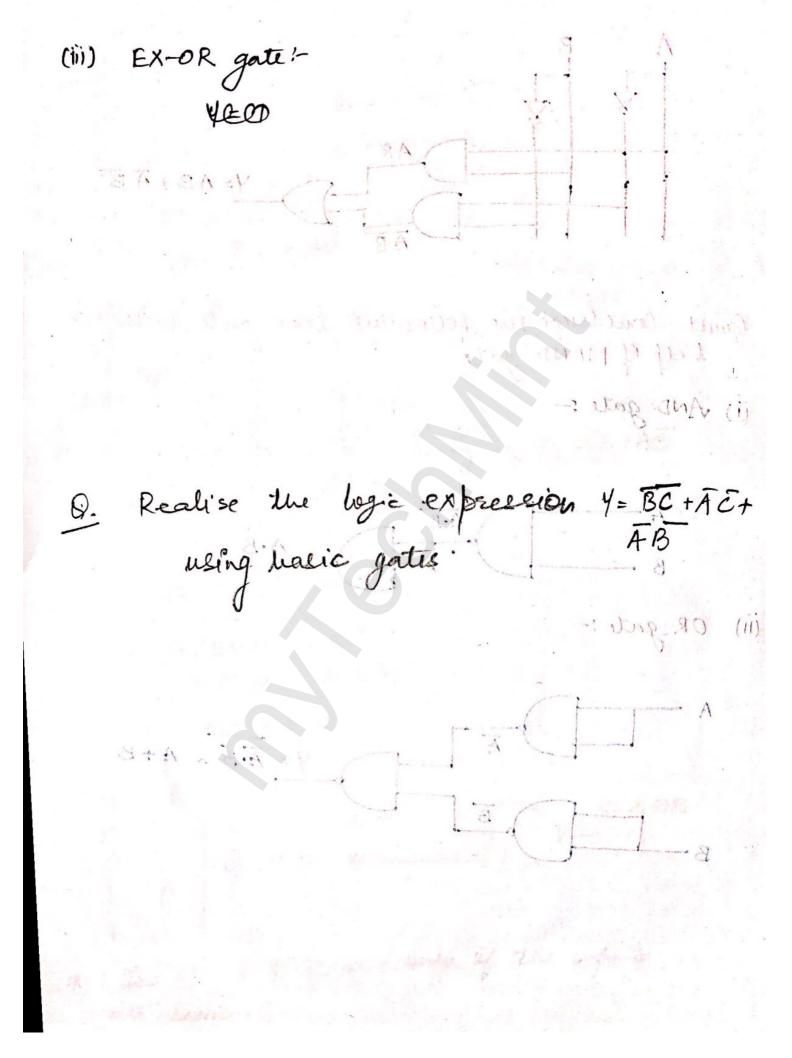

### LOGIC GATES \*

hogic gates are building blocks of any digital system they can be constructed by using simple suitches, relays, diodes, transcitors or integrated circuits It is defined as an Electronic device with logical manipulation and one or more than one inputs and only one output is called logic gate.

\* The logic gates are classified as 1-

U) Basic Gale: - AND Gate OR Gate NOT Gale

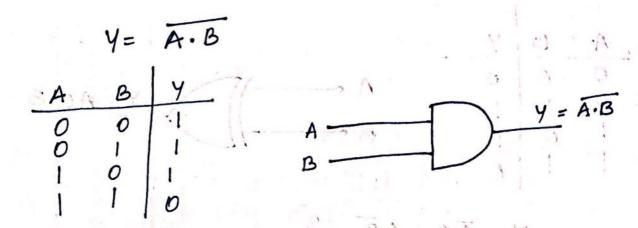

(ii) Universal Gates - NAND gate NOR gate

(111) Special purpose gates :- Exclusine OR gate ... Exclusine NOR gate

\* The ofp of goods AND gate is '1' if and only if are the inputs are at high logic i.e. I

\* The ofp of a NAND gate is I if and only if any one or more than one input at any time is low i.e. at logic o'.

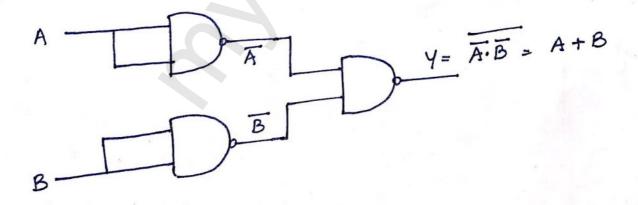

NOR Gate

The NOR gate is basically NOT-OR gate. It is also a surriversal gate

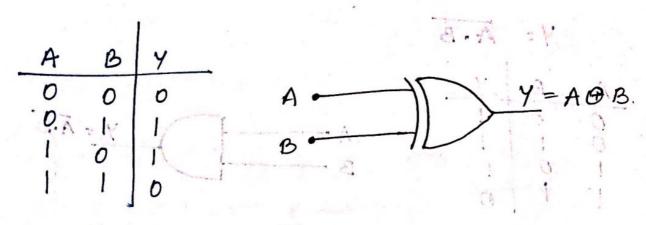

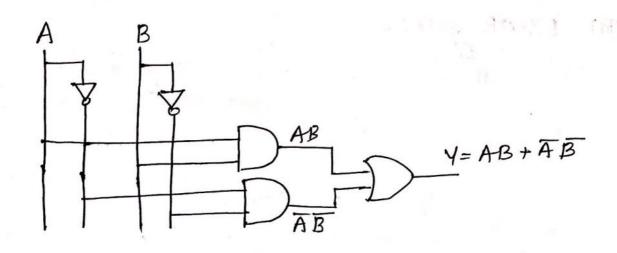

EXCLUSIVE - OR GATE

$$y = \overline{AB + AB}$$

\* The output is I if and only if the inputs are different.

## EXCLUSIVE NOR gate

$$Y = A(EX-NOR)B$$

$$= AOB = \overline{ABB}$$

$$= AB + \overline{AB}$$

\* The eff is I if and only if the inputs are same.

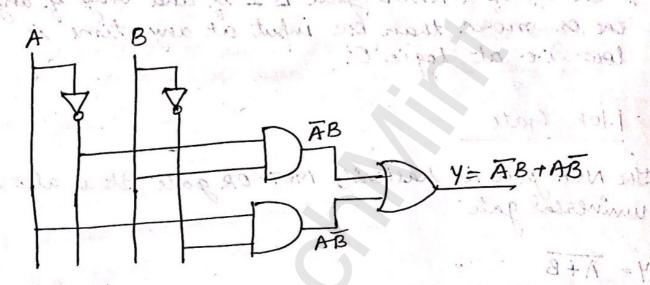

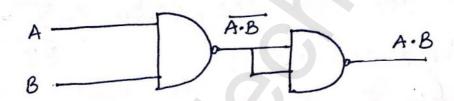

Queel Construct the following logic gates with the help of NAND gate

(i) AND gate:

(ii) OR gate !-

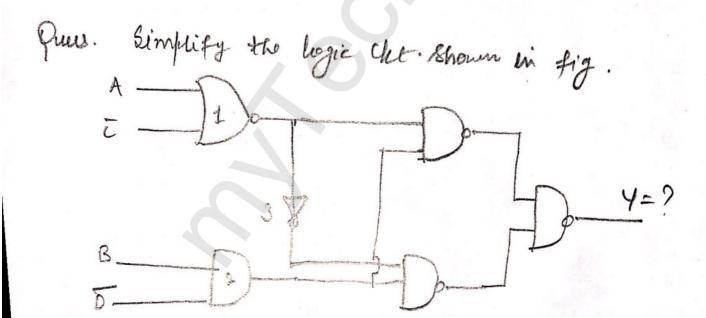

D. Implement  $Y = \overline{AB + A + (B+C)}$  using NAND gates. only.